High-Level Digital Design

Course developed by: Juan Manuel Moreno, Electronic Engineering Dept, UPC

Contact: joan.manuel.moreno@upc.edu

Course Description

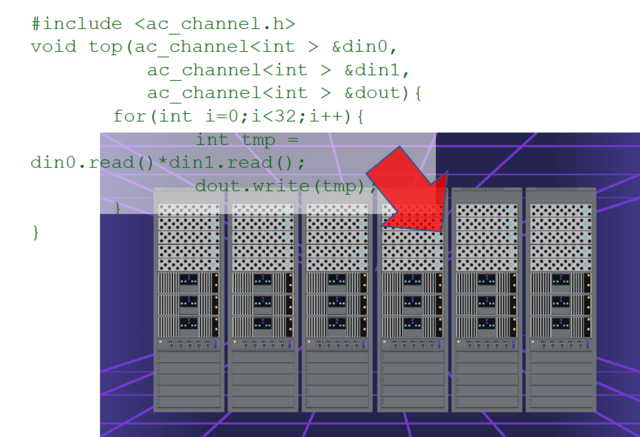

This Master’s course aims that the student understands the implications of hardware/software co-design and the use of configurable integrated systems (SOC), as well as high-level design principles of digital systems based on programmable and configurable components.

The student will use the SystemVerilog hardware description language and the Universal Verification Methodology to carry out the functional verification of complex digital systems. The sustainability implications of the design decisions, as well as techniques to reduce this impact, will also be discussed in this course.

The course also covers the design and implementation, using high-level design languages and techniques, of digital communication and information processing systems, as well as communication interfaces between programmable subsystems (microprocessor/microcontroller) and configurable subsystems (FPGA).

Learning Objectives

By the end of this course, students are able to …

- Understand the implications of hardware/software co-design and the use of configurable integrated systems (SOC).

- Design and implement communication interfaces between programmable subsystems (microprocessor/microcontroller) and configurable subsystems (FPGA).

- Understand the high-level design principles of digital systems based on programmable and configurable components.

- Design and implement, using high-level design languages and techniques, digital communication and information processing systems.

Course access (restricted to UPC enrolled students only)

Open access provided? No

Course duration: ~ 125 hours

Course type: In-class course

Target audience: Students at Masters level

Course language: English

Is this course free? No

Self-paced course? No

Is the certificate / are the credentials free? No

Assessment type: Exams, laboratory assessments