Digital Nanoelectronic Design

Course developed by: Jordi Madrenas and Jordi Cosp, Electronic Engineering Dept, UPC

Contact: jordi.madrenas@upc.edu

Course Description

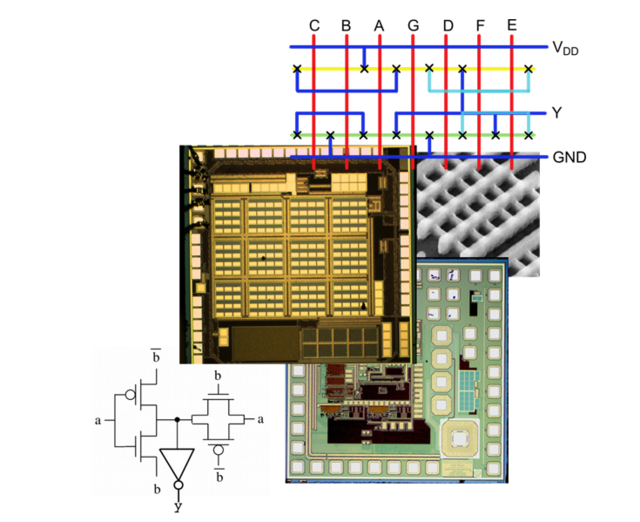

This is a Master’s course aiming the design of digital medium-complexity CMOS integrated circuits, from hardware description to tapeout.

In this course, specific attention will be given to low-power design techniques (dynamic power reduction; clock gating; static power reduction. power gating; dynamic voltage scaling) as well as practical aspects of VLSI design (interconnects; crosstalk; robustness and variability; power supply distribution; clock distribution; buffering; input/output pads; layout and tapeout; packaging).

An introduction to test and verification will be also provided.

Learning Objectives

By the end of this course, students are able to …

- Design digital medium-complexity CMOS integrated circuits, from hardware description to tapeout.

- Understand the evolution of integrated technologies.

- Identify cases and applications suitable for an integrated solution.

- Analyze the characteristics of a digital integrated circuit.

- Introduce low-power design techniques.

- Evaluate the effect of interconnects and to consider them in the design.

- Use ancillary elements, such as power and clock distribution, buffers, PLLs/DLLs, I/O pads and drivers.

- Use industrial CAD/CAE tools for digital integrated design.

Course access (restricted to UPC enrolled students only)

Open access provided? No

Course duration: ~ 125 hours

Course type: In-class course

Target audience: Students at Masters level

Course language: English

Is this course free? No

Self-paced course? No

Is the certificate / are the credentials free? No

Assessment type: Exams, assignments